Chapter 253: ESP32-S3 Architecture and Differences

Chapter Objectives

By the end of this chapter, you will be able to:

- Describe the dual-core Xtensa LX7 architecture of the ESP32-S3.

- Explain the purpose and benefit of the new vector instructions for AI and DSP acceleration.

- Detail the connectivity upgrades, including Bluetooth 5 (LE) and Wi-Fi 4.

- Understand how the ESP32-S3 combines features from the original ESP32 and the ESP32-S2.

- Identify the ideal applications for the ESP32-S3, particularly in the AIoT (Artificial Intelligence of Things) space.

- Write code that queries the S3’s specific hardware capabilities.

Introduction

Having explored the original ESP32‘s dual-core power and the ESP32-S2’s modern I/O and security, we now arrive at the ESP32-S3. This variant can be seen as the culmination of the Xtensa-based ESP32 line, effectively merging the best attributes of its predecessors while adding a powerful new capability: hardware-accelerated machine learning.

The ESP32-S3 brings back the dual-core design, but with the more potent LX7 cores. It retains the native USB OTG from the S2, re-introduces Bluetooth (upgraded to Bluetooth 5 LE), and significantly expands the number of available peripherals. Its headline feature, however, is the inclusion of vector instructions, which transforms the S3 from a general-purpose IoT controller into a formidable edge computing device capable of running lightweight AI models and complex digital signal processing (DSP) algorithms. This chapter dissects the architecture that makes the ESP32-S3 the go-to choice for the next generation of intelligent, interactive, and connected devices.

%%{init: {'theme': 'base', 'themeVariables': {'fontFamily': 'Open Sans, sans-serif'}}}%%

flowchart TB

subgraph "Predecessors"

A(<b>ESP32 Original</b><br>- Dual-Core<br>- Bluetooth)

B(<b>ESP32-S2</b><br>- Powerful LX7 Core<br>- Native USB OTG<br>- RISC-V ULP<br>- Enhanced Security)

end

C(<b>ESP32-S3</b>)

subgraph "Resulting Features in S3"

D(<b>Dual-Core</b> Power<br><i>Upgraded to LX7</i>)

E(<b>Bluetooth 5 LE</b><br><i>Modernized</i>)

F(Native <b>USB OTG</b><br><i>Retained</i>)

G(Easy-to-use<br><b>RISC-V ULP</b><br><i>Retained</i>)

H(<b>AI Vector Extensions</b><br><i><b style="color:#059669;">NEW!</b></i>)

end

A -- "Dual-Core Concept" --> D

A -- "Bluetooth Concept" --> E

B -- "LX7 Core & USB OTG" --> F

B -- "ULP & Security Model" --> G

D -- " " --- C

E -- " " --- C

F -- " " --- C

G -- " " --- C

H -- " " --- C

%% Styling %%

classDef esp32 fill:#FEE2E2,stroke:#DC2626,stroke-width:1px,color:#991B1B;

classDef esp32s2 fill:#DBEAFE,stroke:#2563EB,stroke-width:1px,color:#1E40AF;

classDef esp32s3 fill:#D1FAE5,stroke:#059669,stroke-width:2px,color:#065F46;

classDef feature fill:#FEF3C7,stroke:#D97706,stroke-width:1px,color:#92400E;

class A esp32;

class B esp32s2;

class C esp32s3;

class D,E,F,G,H feature;

Theory

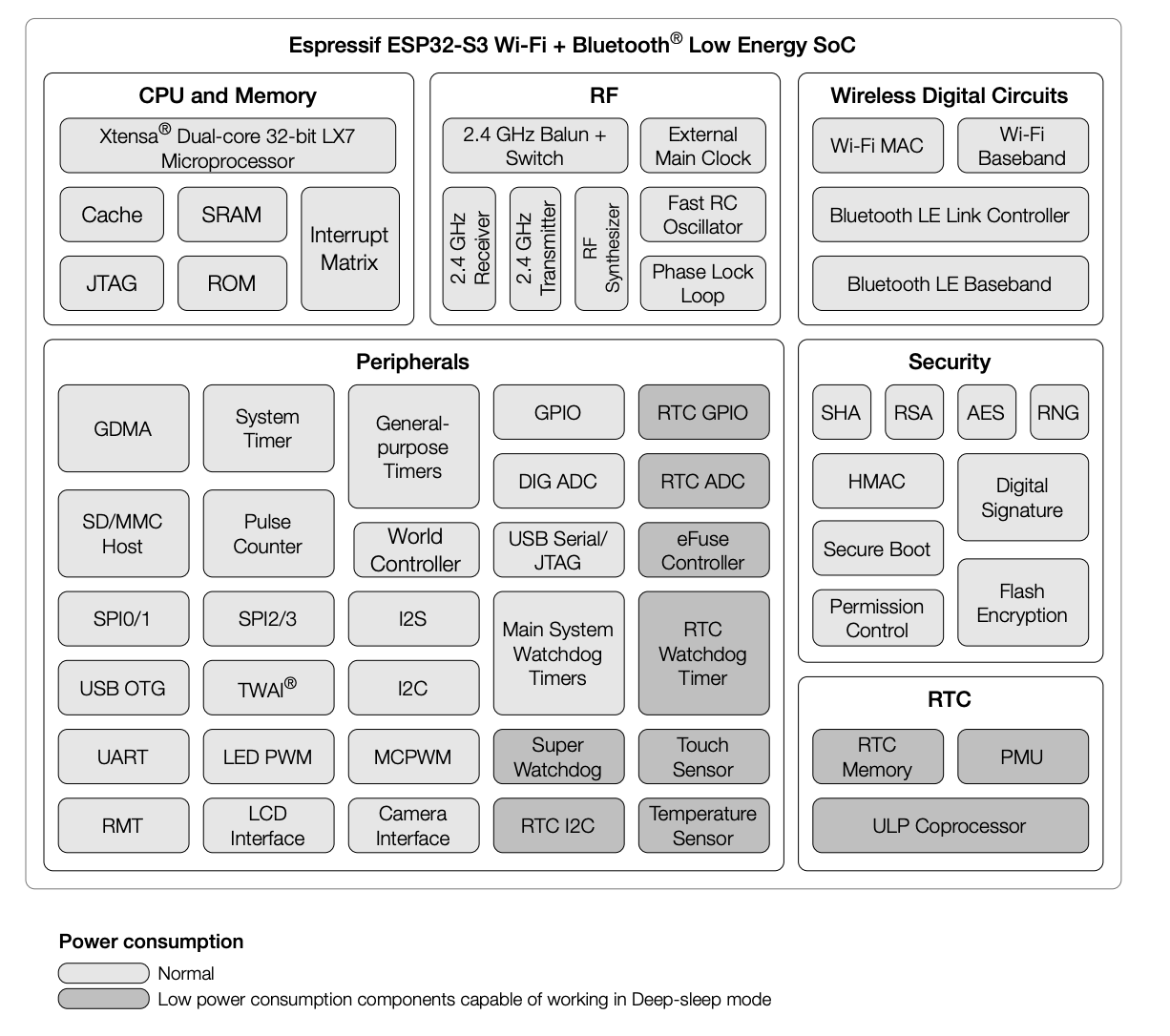

The ESP32-S3 architecture is a strategic evolution, designed to handle more demanding workloads like voice recognition, image processing, and sensor data analysis right at the edge.

1. CPU and AI Acceleration

- Dual-Core Xtensa LX7: The S3 returns to a dual-core configuration, but it upgrades both cores to the Xtensa LX7 platform. This provides both the raw performance of a high-speed (up to 240 MHz) core and the true parallelism of a symmetric multiprocessing (SMP) system. The Wi-Fi and Bluetooth stacks are typically handled by Core 0, leaving the entire power of Core 1 for demanding user applications.

- Vector Instructions for AI/DSP: This is the S3’s most significant architectural enhancement. The LX7 cores include extensions for processing vectors of data. These are a form of SIMD (Single Instruction, Multiple Data) processing.

Analogy: AI Acceleration

Imagine you have eight letters to capitalize. A standard CPU (scalar processor) would pick up one letter, capitalize it, put it down, and repeat the process eight times. An S3 core with vector instructions (vector processor) can pick up all eight letters at once, capitalize them in a single operation, and put them all down. This is vastly more efficient for repetitive mathematical operations that are common in AI neural networks and DSP algorithms (like filters and transforms).

%%{init: {'theme': 'base', 'themeVariables': {'fontFamily': 'Open Sans, sans-serif'}}}%%

graph TD

subgraph "Standard CPU (Scalar)"

direction TB

A[Start] --> B(Op 1: Capitalize 'h')

B --> C(Op 2: Capitalize 'e')

C --> D(Op 3: Capitalize 'l')

D --> E(Op 4: Capitalize 'l')

E --> F(...)

F --> G[End: 8+ Operations]

end

subgraph "ESP32-S3 CPU (Vector / SIMD)"

direction TB

H[Start] --> I{"<b>Single Instruction:</b><br>Capitalize ['h','e','l','l','o','w','o','r']"};

I --> J[End: 1 Operation]

end

%% Styling %%

classDef start fill:#EDE9FE,stroke:#5B21B6,stroke-width:2px,color:#5B21B6;

classDef endo fill:#D1FAE5,stroke:#059669,stroke-width:2px,color:#065F46;

classDef process fill:#DBEAFE,stroke:#2563EB,stroke-width:1px,color:#1E40AF;

classDef vector fill:#FEF3C7,stroke:#D97706,stroke-width:2px,color:#92400E;

class A,H start;

class G,J endo;

class B,C,D,E,F process;

class I vector;

These instructions are leveraged by Espressif’s libraries, most notably ESP-NN (Neural Network) and the ESP-DSP library, to achieve performance boosts of an order of magnitude or more for supported operations compared to standard C implementations.

2. Connectivity: Bluetooth 5 is Back

- Wi-Fi 4: The S3 includes the same reliable Wi-Fi 4 (802.11 b/g/n) radio as its predecessors.

- Bluetooth 5 (LE): Recognizing the importance of smartphone connectivity and low-power peripherals, the S3 brings back Bluetooth. It features a modern Bluetooth 5 (LE) radio. This provides key advantages over the ESP32’s v4.2 radio, including support for higher data rates (2Mbps PHY), longer range (LE Coded PHY), and extended advertising capabilities.

Warning: The ESP32-S3 supports Bluetooth LE only. It does not include a radio for Bluetooth Classic (e.g., for legacy SPP or A2DP audio streaming profiles). For Bluetooth Classic, the original ESP32 is still the required choice.

3. Memory and I/O

The S3 is designed to handle larger, more complex applications.

- Memory: It is equipped with 512 KB of internal SRAM, providing ample space for application data, network buffers, and the AI model’s working memory (arena). It also supports high-speed Quad SPI communication with external PSRAM and Flash.

- USB OTG: The S3 retains the full-speed USB 2.0 OTG interface from the S2, enabling it to function as a native USB device or host.

- Expanded Peripherals: The S3 has one of the most generous peripheral sets in the ESP32 family, with up to 45 physical GPIO pins and a large number of configurable SPI, I2C, and UART interfaces, making it suitable for complex products with many external components.

- ULP Coprocessor: Like the S2, the S3 includes the easy-to-program RISC-V ULP coprocessor for low-power sensor monitoring.

Practical Examples

Let’s write a program that inspects the S3’s hardware and reports its capabilities, confirming the features we’ve just discussed.

Example 1: Hardware Capability Reporter

This example uses ESP-IDF helper functions to print out the chip’s core count, revision, and whether it has the specific features we expect, like Bluetooth and the AI/DSP acceleration extensions.

1. Code: Create a new project in VS Code targeting the ESP32-S3 and use the following code in main.c.

#include <stdio.h>

#include "freertos/FreeRTOS.h"

#include "freertos/task.h"

#include "esp_log.h"

#include "esp_chip_info.h"

#include "esp_idf_version.h"

static const char *TAG = "S3_REPORTER";

void app_main(void)

{

ESP_LOGI(TAG, "ESP32-S3 Hardware Capability Reporter");

ESP_LOGI(TAG, "ESP-IDF Version: %s", esp_get_idf_version());

// Structure to hold chip information

esp_chip_info_t chip_info;

// Populate the structure

esp_chip_info(&chip_info);

ESP_LOGI(TAG, "Chip model: ESP32-S3");

ESP_LOGI(TAG, "Silicon revision: %d", chip_info.revision);

ESP_LOGI(TAG, "Number of CPU cores: %d", chip_info.cores);

// Check for specific hardware features using the features bitmask

ESP_LOGI(TAG, "--- Feature Check ---");

if (chip_info.features & CHIP_FEATURE_WIFI_BGN) {

ESP_LOGI(TAG, "[+] Wi-Fi 4 (802.11b/g/n) supported.");

}

if (chip_info.features & CHIP_FEATURE_BLE) {

ESP_LOGI(TAG, "[+] Bluetooth LE supported.");

}

if (chip_info.features & CHIP_FEATURE_BT) {

ESP_LOGW(TAG, "[!] Bluetooth Classic NOT supported.");

} else {

ESP_LOGI(TAG, "[+] No Bluetooth Classic radio, as expected.");

}

// The S3's AI acceleration is via DSP and NN instructions in the LX7 core.

// While there isn't a single "CHIP_FEATURE_AI", we know the S3 has it.

// For projects, you'd enable CONFIG_ESP_DSP_SMALL_TAKE_BIG_IRAM in menuconfig.

ESP_LOGI(TAG, "[+] Core includes vector instructions for AI/DSP acceleration.");

ESP_LOGI(TAG, "---------------------");

// Let's prove it's a dual-core system by running a task on the other core

xTaskCreatePinnedToCore(

[](void *pvParameters) {

ESP_LOGI(TAG, "This message is from a task running on Core %d", xPortGetCoreID());

vTaskDelete(NULL);

},

"OtherCoreTask",

2048,

NULL,

5,

NULL,

1 // Pin to Core 1

);

}

2. Build and Flash:

Use the standard “ESP-IDF: Build, Flash and Monitor” command. An ESP32-S3 board in its normal running state can typically be flashed directly without needing to manually enter bootloader mode.

3. Observe:

The monitor output will confirm the S3’s architecture, showing two cores, support for BLE, and our explicit log about AI acceleration. You will see the log message from the task running on Core 1, proving the dual-core system is active.

I (298) S3_REPORTER: ESP32-S3 Hardware Capability Reporter

I (308) S3_REPORTER: ESP-IDF Version: v5.x.x

I (308) S3_REPORTER: Chip model: ESP32-S3

I (318) S3_REPORTER: Silicon revision: 0

I (328) S3_REPORTER: Number of CPU cores: 2

I (328) S3_REPORTER: --- Feature Check ---

I (338) S3_REPORTER: [+] Wi-Fi 4 (802.11b/g/n) supported.

I (348) S3_REPORTER: [+] Bluetooth LE supported.

I (358) S3_REPORTER: [+] No Bluetooth Classic radio, as expected.

I (368) S3_REPORTER: [+] Core includes vector instructions for AI/DSP acceleration.

I (378) S3_REPORTER: ---------------------

I (378) main_task: Task[OtherCoreTask] created on Core 1

I (388) S3_REPORTER: This message is from a task running on Core 1

Variant Notes

The ESP32-S3 is the most feature-rich Xtensa-based variant, making it a clear upgrade path for many projects.

| Feature / Variant | ESP32 (Original) | ESP32-S2 | ESP32-S3 | ESP32-C3 / C6 |

|---|---|---|---|---|

| CPU Core(s) | Dual-Core LX6 | Single-Core LX7 | Dual-Core LX7 | Single-Core RISC-V |

| AI Acceleration | No | No | Yes (Vector Instr.) | No |

| Bluetooth | Classic + BLE 4.2 | No | BLE 5.0 | BLE 5.0 |

| USB | No (UART bridge) | Yes (OTG) | Yes (OTG) | No (UART bridge) |

| SRAM | 520 KB | 320 KB | 512 KB | 400 KB |

| GPIOs (Max) | ~34 | ~43 | ~45 | ~22 |

| Primary Focus | General Purpose | Low-Power, HMI | AIoT, Rich HMI | Cost-Effective IoT |

Common Mistakes & Troubleshooting Tips

| Mistake / Issue | Symptom(s) | Troubleshooting / Solution |

|---|---|---|

| Ignoring AI/DSP Libraries | Math-heavy code (NN, FFTs) runs much slower than expected; no performance gain over older chips. | Use the right libraries. You must use ESP-NN for neural networks or ESP-DSP for signal processing to leverage the hardware vector instructions. Standard C code will not be accelerated. |

| Forgetting Dual-Core Sync | Data corruption, unpredictable behavior, or crashes when two tasks access the same variable or peripheral. | Protect shared resources. Use synchronization primitives like mutexes for shared memory or thread-safe queues for inter-core communication. Assume nothing is safe unless proven otherwise. |

| Assuming BT Classic Support | Compiler errors when including esp_bt_main.h. A2DP or SPP profile code fails to link or initialize. | Use the original ESP32 for BT Classic. The S3 only supports Bluetooth 5 LE. Design new applications around modern LE profiles or use the original ESP32 if legacy support is mandatory. |

Exercises

- ESP-NN Library Exploration: Download the

esp-whorepository from Espressif, which contains many AI examples. Find theimage_recognitionexample for the ESP32-S3. Without needing a camera, build and flash the application. Observe the logs to see how the ESP-NN library is initialized and how it runs a classification model (like MobileNet) using the S3’s accelerated instructions. This exercise is about exposure to a real-world AI application structure. - Dual-Capability Device: Create an application that showcases the S3’s versatility. The device should use the USB CDC interface to accept commands from a serial monitor.

- If the user types

temp, the device should use BLE to advertise a simulated temperature reading (e.g., “TEMP:23.5C”) for 30 seconds. - If the user types

info, the device should print the hardware capability report from our practical example to the USB console.

- If the user types

Summary

- The ESP32-S3 is the flagship Xtensa-based variant, featuring a powerful dual-core LX7 CPU running up to 240 MHz.

- Its key differentiator is the inclusion of vector instructions for AI and DSP acceleration, making it ideal for edge machine learning applications.

- It combines the best of its predecessors: dual-core processing, native USB OTG, and robust connectivity with Wi-Fi 4 and Bluetooth 5 (LE).

- With 512 KB of SRAM and up to 45 GPIOs, it can handle complex applications with rich human-machine interfaces.

- The ESP32-S3 is the premier choice for developing advanced AIoT products, including voice assistants, smart displays, and intelligent sensors.

Further Reading

- ESP32-S3 Technical Reference Manual: The complete and official hardware reference for the S3.

- ESP-NN Library Documentation: The official guide for using the neural network acceleration library.

- ESP-DSP Library Documentation: The official guide for the digital signal processing library.